2. Основные сведения о VHDL

Использование графического представления схем из логических элементов может быстро перегрузиться и усложнить восприятие даже с использованием обозначений некоторых абстрактных элементов с заранее известным поведением. Для улучшения эффективности разработки логических схем были созданы системы автоматического проектирования (САПР), которые позволили использовать языки описания аппаратуры (англ. Hardware Description Language, HDL). То есть, были разработаны инструменты, благодаря которым описания поведения схем стало превращаться в схемы. Этот процесс называется синтезом. Синтез является одним из этапов компиляции проектов под ПЛИС; ступени компиляции проектов мы рассмотрим немного позднее.

Итак, для получения схемы теперь достаточно её описать. Для описания схем в рамках данного конспекта будет рассматриваться язык VHDL, а именно его наиболее актуальную версию VHDL 2008. \

!NB Важный факт о VHDL: язык является нечувствительным к регистру, то есть объекты с именами Var1 и VAR1 — это один и тот же объект.

Структура описания схемы на VHDL выглядит следующим образом:

- Подключаемые библиотеки

- Описание сущности (англ. entity)

- Описание архитектуры

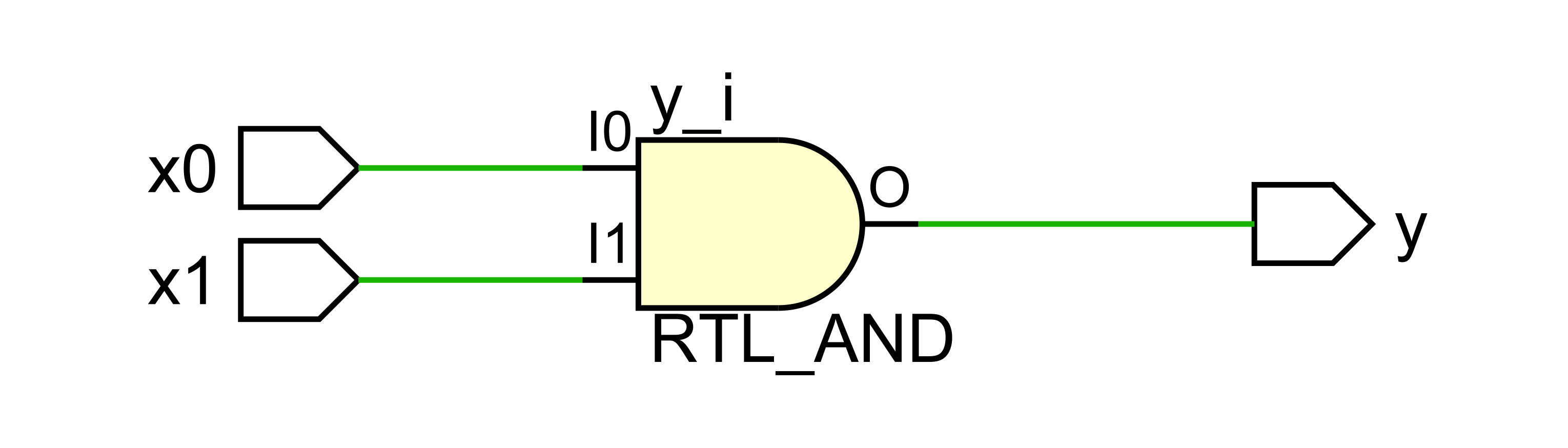

Рассмотрим каждый из элементов отдельно на примере описания элемента И, представленного ниже. Если текст начинается с двойного дефиса — это комментарий к коду.

Библиотека IEEE — это набор стандартных объектов языка описания, которые утверждены международным институтом электроинженерии. STD_LOGIC_1164 подключается для того, чтобы воспользоваться необходимыми типами данных и возможными операциями над ними. В VHDL один из наиболее распространенных является тип std_logic. Его название буквально означает "стандартная логика". Этот тип определяет возможные логические значения, такие как логический ноль и логическую единицу. Подробнее об этом типе будет описано в следующих разделах.

Поле entity предназначено для описания программу как черного ящика, как ее мог бы видеть пользователь этой схемы. В ней содержится поле port, в нем определяются входы, выходы и их параметры. В данном примере система имеет два однобитных входа и один выход, все инициализированы типом std_logic.Обратите внимание - так как запись по сути является перечислением в скобках, то после последней записи отсутствует точка с запятой - это частая орфографическая ошибка у начинающих.

Блок архитектура (architecture) своим названием отражает свое назначение: в нем производится описание архитектуры программы. Внутри архитектуры между ключевыми слова begin и end описывается поведение схемы. В представленном коде демонстрируется простое описание путем присвоения в выход логической схемы результата логической операции И над двумя входами схемы. В языке VHDL символы "<=" подразумевают операцию присвоения, называемой неблокирующее присваивание (Nonblocking Assignment).

В результате анализа данного описания САПР Vivado превратит его в следующую схему:

Результат компиляции кода

В языке VHDL существует набор зарезервированных слов, которые обозначают логические операции, вот некоторые из них:

| конструкция в VHDL | описание |

|---|---|

not

|

НЕ |

and |

И |

or |

ИЛИ |

xor |

Исключающее ИЛИ |

Используя их можно буквально описывать уравнениями необходимые логические схемы. При их использовании необходимо учитывать порядок выполнения операций, который задается с помощью скобок. Например:

... 1 architecture mux_struct of mux1 is 2 begin 3 y <= x0 and x1; 4 y2 <= (x0 and not(a)) or (x1 and a); 5 end mux_struct;