Основы VHDL

7. Конструкция process

7.2. Триггер на VHDL

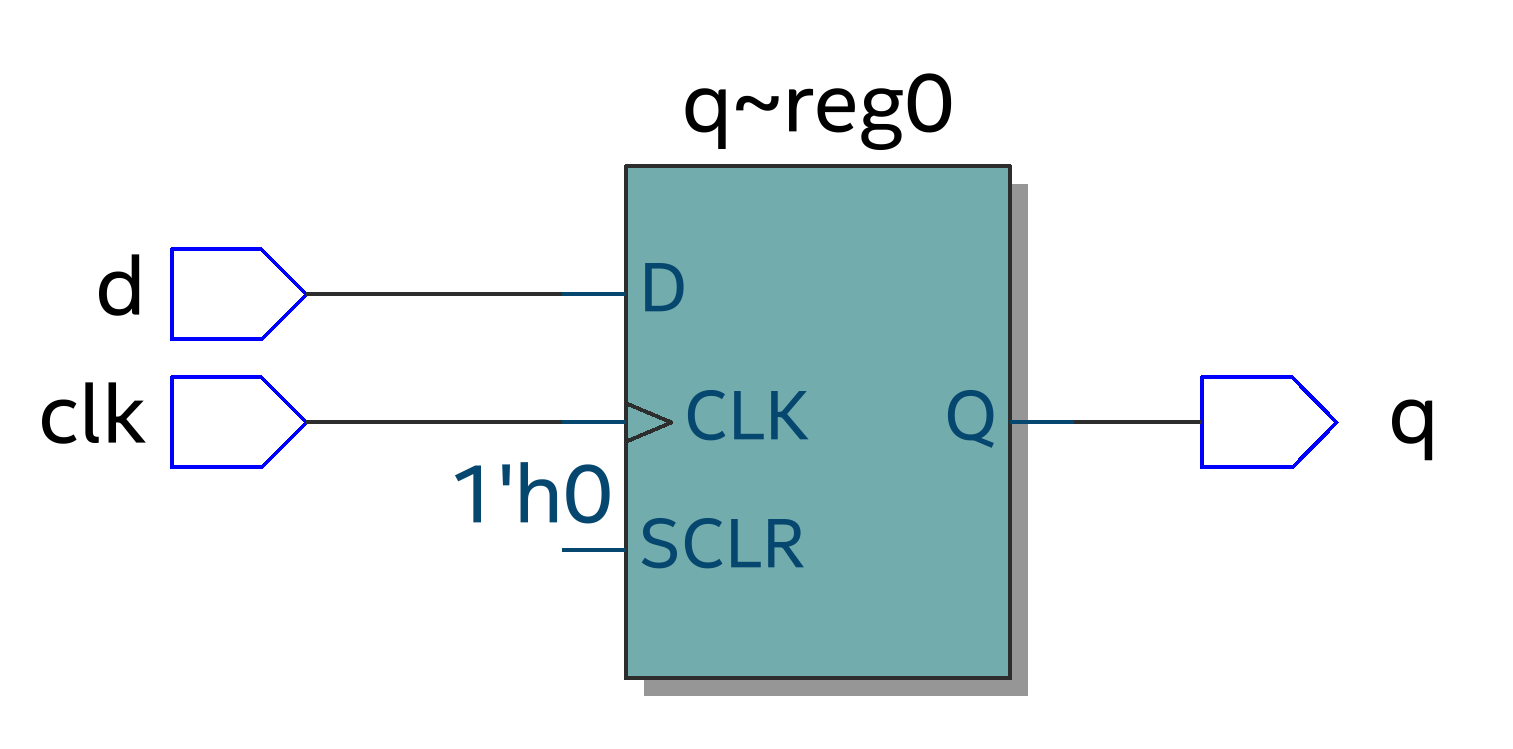

По аналогии с защелкой в условии ветвления можно использовать функцию rising_edge(clk) — эта функция возвращает состояние истины только в момент положительного перепада фронта сигнала clk. Простое описание триггера может выглядеть следующим образом:

В рамках этой конструкции можно добавить функционал комбинационных схем и начать реализовывать описание более сложных систем: счетчиков, конвейерных вычислений, детекторов событий и многих других. Ниже приведены примеры в обратном порядке: сначала задача и схема, которую может выполнить данную задачу, а затем код, с помощью которого можно синтезировать данную схему.

Сдвиговый регистр

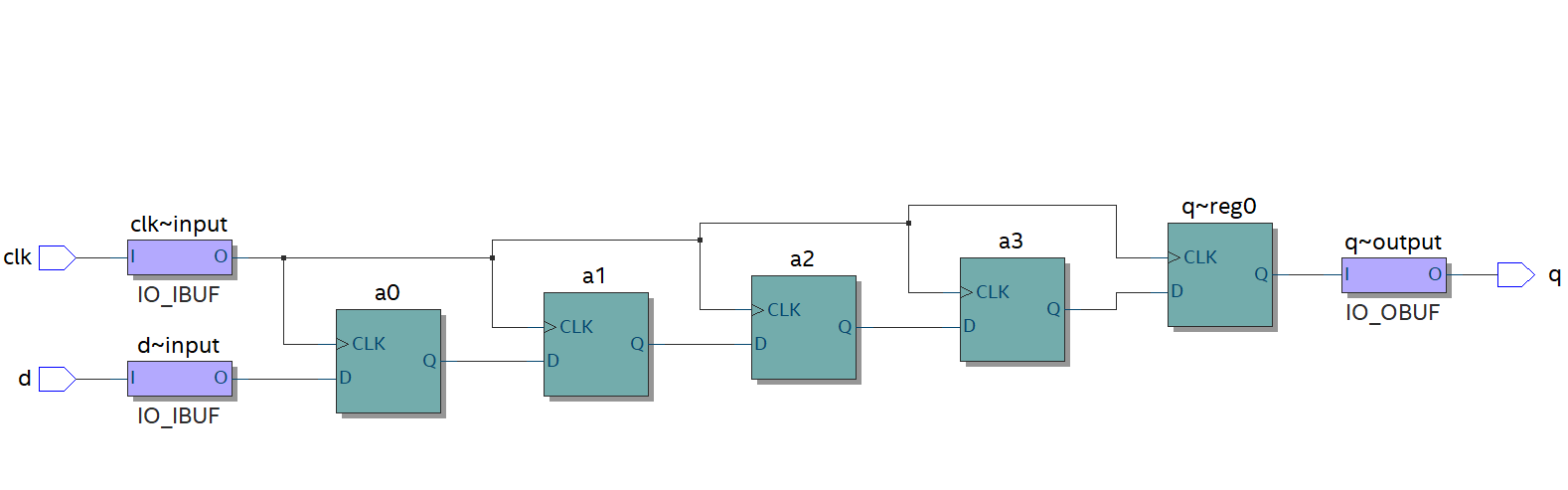

Одна из наиболее стандартных визуализаций последовательной логики — это сдвиговый регистр: цепь последовательно соединенных друг за другом триггеров, фактически задерживающие распространение изменяющегося сигнала на входе первого триггера на время, равное длительности периода тактовой частоты умноженной на количество регистров в цепи. Подробнее можно поиграться со схемой на сайте: https://www.falstad.com/circuit/, выбрал Схемы ->Последовательные схемы -> Сдвиговые регистры -> SIPO. Пример такой схемы показан ниже ( можно не обращать внимания на буферы входов и выходов — это просто компоненты представления схемы после Technology map)

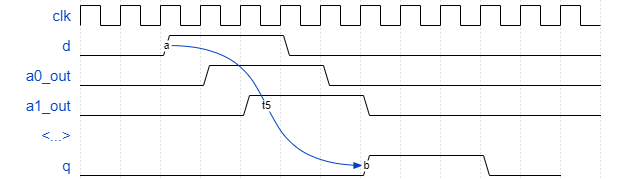

Поведение компонентов схемы можно описать временной диаграммой:

С каждым тактом генератора изменение на входе распространяется к выходу схемы, пока, наконец, через 5 тактов не проявится.

Простая версия исходного кода может выглядеть следующим образом:

В данном случае передача данных из "провода" а1 в "провод" а2 происходит только положительному фронту, что архитектурно подразумевает наличие триггера между этими проводами.

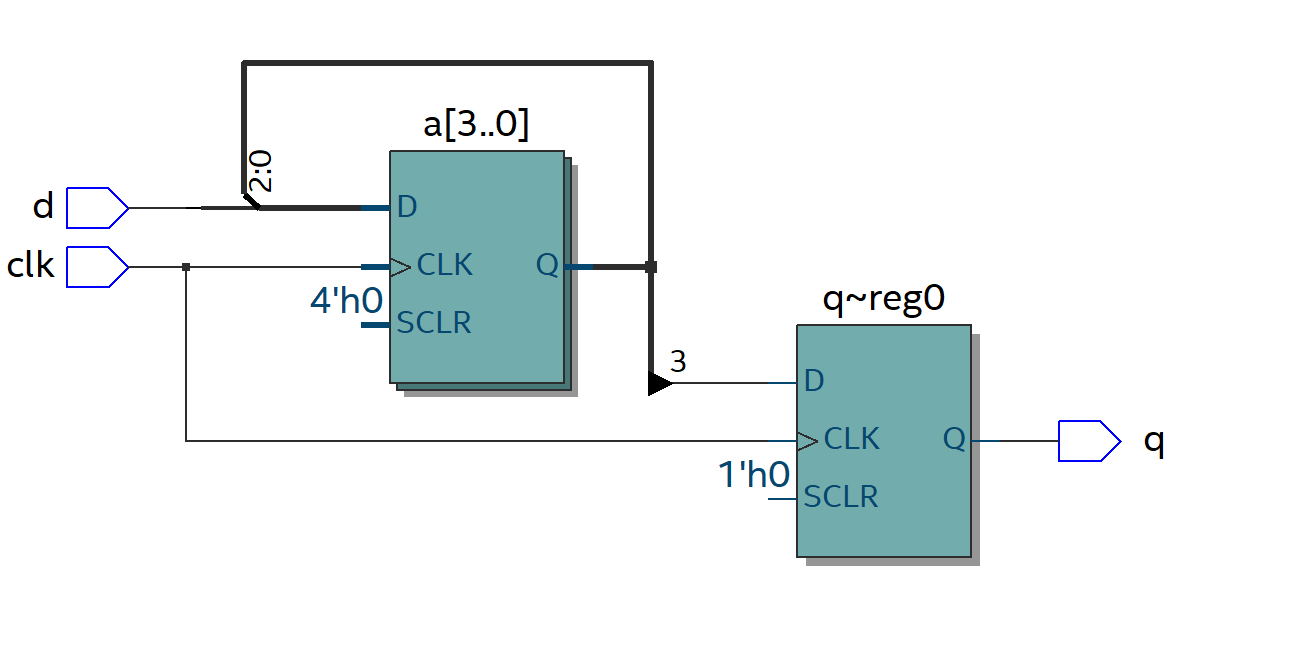

Выше приведена схема потому что визуальное представление на RTL Viewer имеет менее визуально очевидные межсоединения:

Здесь уже изображена "пачка" триггеров, назначенных на каждый "слой" из изображения выше. Эту же запись можно проинтерпретировать как попросту многобитное слово, внутри которого производится сдвиг каждого бита вправо или влево, а крайние значения отвечают за вход и выход. Пример такого решения с возможностью параметризации: